### High Performance (Scientific) Computing: from your desktop PC to parallel supercomputers A user-friendly introduction

Michele Griffa PhD student, XIX cycle

Dept. of Physics, Politecnico di Torino corso Duca degli Abruzzi 24, 10129, Torino (Italy) and Bioinformatics and High Performance Computing Laboratory Bioindustry Park of Canavese via Ribes 5, 10010, Colleretto Giacosa (Italy)

E-mail: <u>michele.griffa@polito.it</u> Personal Web site: <u>http://www.calcolodistr.altervista.org</u>

16/10/06

### **Table of contents**

- 1 Introduction

- 2 High Performance Computing (HPC): what does it mean and why do we need it ?

- 3 Computers architectures

- 3.1 The Von Neumann's architecture and its bottlenecks

- 3.2 CPU built-in parallelism: technological improvements

- 3.2.1 Bit-parallel memory and arithmetic

- 3.2.2 Implementation of I/O-dedicated processors

- 3.2.3 Memory interleaving

- 3.2.4 Hierarchies of memories

- 3.2.5 Multitasking

- 3.2.6 Instructions look-ahead

- 3.2.7 Multiple functions units

- 3.2.8 Pipelining

- 3.2.9 Floating point arithmetic: SSE technology

- 3.2.10 CPU design "philosophies": past and future sceneries

- 3.2.10.1 CISC and RISC architectures

- 3.2.10.2 VLIW (Very Long Instruction Word) CPUs: 64-bits architectures

- 3.2.10.3 SMP (Symmetric Multiprocessor) and Multi-Cores computers

- 3.3 Parallel (multiprocessor) computers

- 3.3.1 SIMD systems

- 3.3.2 MIMD systems

- 3.3.2.1 Shared-memory architectures

- 3.3.2.2 Distributed-memory architectures

- 3.3.3 Interconnetion issues

- 3.4 Grid Computing: the future of HPC ?

- 4 1<sup>st</sup> level of HPC: optimization of scalar codes (squeezing the hardware of your desktop PC !)

- 4.1 Profiling your programs

- 4.1.1 Example of software for performance analysis

- 4.2 Source-code level optimization

- 4.3 Assembly-code level optimization by compilers

- 4.4 The Intel Fortran-C/C++ Linux compiler for x86/x86\_64 architectures as an example of optimal compiler for Intel architectures

- 5 2<sup>nd</sup> level of HPC: parallel programming for parallel computers

- 5.1 Parallel programming paradigms

- 5.1.1 Message passing paradigm

- 5.1.1.1 MPI libraries

- 5.1.2 Shared-memory systems paradigms

- 5.1.2.1 OpenMP6 Concluding remarks and aknowledgements

- 7 Bibliography

- 8 List of useful Web sites

Group picture of the teachers (red numbers) and participants to the 13<sup>th</sup> Cineca Summer School on Parallel Computing. Instructors: (1) Sigismondo Boschi, (2) Carlo Cavazzoni, (3) Cristiano Calonaci, (4) Claudio Gheller, (5) Gerardo Ballabio. Giovanni Erbacci and Chiara Marchetto (the other teachers) were not present in this photo. Green arrow (and green t-shirt): me. Many thanks to C. Calonaci and Cineca Web Administrators for having recovered this photograph.

Group picture of the teachers (red numbers) and participants to the 2<sup>nd</sup> Caspur Summer School on Advanced HPC. Instructors: (1) Federico Massaioli, (2) Giorgio Amati, (3) Gabriele Mambrini, (4) Roberto Verzicco, (5) Jack Dongarra. (6) Elena ?????. The other teachers of the School were not present in this photo. Green arrow (but white t-shirt, this time): me.

#### 1. Introduction

This document is a brief and incomplete report on the art of **High Performance** (Scientific) **Computing (HPC)** targeted to Scientists (certainly not to Computer Scientists or Computational Scientists). Its main objective is to give the interested non-specialist reader an overview on how to improve the performance of his/her computing codes used in his/her scientific day-work. Performance does not mean only speed of execution. Indeed, high performance is concerned with the trade-off between speed, machine workload, volatile/hard memory occupation.

This report should show that for improving the performance of one's scientific computing code it is not necessary or sufficient to have high performance hardware facilities: algorithms design, methods and approaches in the implementation of the code with a programming language, customization of the code according to hardware features are important issues yet.

Section 2 presents a brief introduction to the world of HPC, with an example of real-world computing problem that for being solved requires computing resources that nowadays are still not available. This is an example of grand-challenge problem and it is useful in showing the importance of HPC in every-days human activities.

Section 3 is completely dedicated to computers architectures with a specific logical flow that starts from the basic ingredients of the Von Neumann architecture (the basic logical model for a sequential electronic computer) and arrives at the main architectures of nowadays parallel supercomputers. The intermediate path covers, in a chronological and logical way, the main important steps that has led from single desktop PCs to parallel architectures, with a particular attention to the hardware technological solutions that have tried to introduce parallelism also within the way of operating of a single CPU. Section 3.1 is dedicated to the Von Neumann architecture of a serial computer with a single processing unit (CPU) and its bottlenecks. Section 3.2 is a temptative and incomplete presentation of the evolution of CPU architectures and technologies that have tried to improve their performances, with a stress on technological solutions to implement parallelism within a single processing unit. This choice of concentrating the attention on such issue is in contrast with usual treatments and presentations within non-specialized mass-media contexts, which tend to emphasize the great and powerful increase of CPU speed in terms of number of clock cycles per unit of time (clock frequency). As it might be shown in Section 3.2, the fantastic improvements in CPU performances are not only based on the increase in CPU speed but also on other technical solutions to exploit parallelism. The famous Moore's law, which has seemed to govern the developments of microelectronics in the last three decades and to be at the basis of every leap forward in computing power, is not all the world ! This fact has been getting very clear to hardware and software manufacturers in the last years: physical limits to device integration at the micron scales have been reached, although nanotechnologies promise to beat new limits. However, parallelism seems nowadays to be the only possible solution to maintain a positive rate for computing power. Section 3.3 is dedicated to multiprocessor computers, with a brief overview of the different vpes of architectures and technological solutions to realize them. This part concludes with a brief presentation of Grid Computing, as a kind of parallel computing solution, its promises and its limits.

Section 4 and 5 are entirely dedicated to HPC with the point of view of a user who wants to obtain the best performance from the facilities he/she has, being them a single commodity PC or a big parallel supercomputer.

Section 4 consists in a collection of treatments and tricks to improve the performance of one's computing codes on a single desktop PC, trying to show that off-the-shelf CPUs have many resources that could be exploited to obtain great results in scientific computing. HPC can just be obtained, firstly, for serial codes running on off-the-shelf desktop PCs: the report considers some aspects of code optimization, using all the resources of the serial PC. In Section 4.2, some general rules are considered in order to improve the performance of the serial code according to general features common to nowadays CPUs architectures available on the desktop market. I treat here only the x86 architectures, also known as IA\_32 (32 bit architectures), of modern CPUs. Since 2004, x86\_64 (64 bit architectures) CPUs have been available on the high-level desktop market. Nowadays, they are commonly used on all categories of computers, from desktop to mobile, from servers to clusters. 64 bit CPUs compatible with the IA\_32 instruction set (firstly introduced by AMD then by Intel, implemented in Pentium IV from the Proconona version) improve performance in fixed point and floating point arithmetics and, more important, can address RAM memories larger than 4 GiBytes, which is the main objective they have been designed for. Although, x86\_64 CPUs are the standard in the design of nowadays multiprocessor supercomputers, the optimization of code running of them require additional knowledge of hardware features which are beyond the scope of this report. Anyway, some of the considerations presented below for x86 architectures remain valid for x86\_64 ones.

In Section 4.3, other types of optimization operations and methods are described, which can be realized not at the source code level but at the Assembly code level, using specific option flags implemented in modern compilers. I consider there and along the whole report the GNU/Linux OS as the standard environment of work and the GCC (GNU Compiler Collection, version 4.1.1) as the standard compiler set therein. This choice is motivated by the fact that GNU/Linux OSs and software are *de facto* the standard tools for Scientific Computing, particularly for cluster

computing. Section 4.4 introduces some features of the Intel Fortran-C/C++ compiler, which is released by Intel freely according to a non-commercial license for personal use. This compiler is optimized for Intel CPU architectures and is a good example of a tool for improving the performance of serial codes according to the specific hardware features of the CPU in use.

When scaling issues imply that the resources of a single PC are not sufficient for a real-world execution of the code, it is necessary to implement a parallel version of the code, to be run on multiprocessor computers. This report is concerned with architectures of parallel supercomputers, including clusters of distributed heterogeneous PCs which are often called as resources of *Grid Computing*. In Section 5.1, the two main parallel programming paradigms are considered along with the corresponding most common and used softwares/methods of implementation developed in the last decades.

After some concluding remarks in Section 6 and a brief Bibliography/list of resources in Section 7, I present a collection of useful WWW resources (links) on parallel computing and more general on HPC in Section 8.

This report is based on knowledge and documentations that I have been collecting since 2004, when I attended the 13<sup>th</sup> edition of the Summer School on Parallel and High Perfomance Computing at <u>Cineca</u> (Consorzio InteruNiversitario per l'Elaborazione e il Calcolo Automatico), placed in Casalecchio di Reno (Bologna). The school is organized every year for University, undergraduates and graduate students and is dedicated to a general introduction into HPC, including parallel computing. The school lasts two weeks (8 hours/day) and for me it was the first occasion for learning about HPC. Part of the material presented below is based on the slides and documents of the school, so I am very grateful to Dr. G. Erbacci, who leads the HPC division of SAP Department of Cineca, and to the other teachers of the school (Dr. G. Ballabio, Dr. S. Boschi, Dr. C. Calonaci, Dr. C. Cavazzoni, Dr. C. Gheller, Dr. A. Guidazzoli, Dr. C. Marchetto), most of all belonging to the same Department.

I also attended the 2<sup>nd</sup> edition of the <u>CASPUR</u> (Consorzio per le Applicazioni del Supercalcolo per l'Università e la Ricerca) Summer School on Advanced HPC, held in Villa Montecucco, Castel Gandolfo (Roma), from August 28<sup>th</sup> to September 8<sup>th</sup> 2006, which was truly inspiring and useful in extending my HPC knowledge and skill. Part of the material present in this report is based on the lectures of this School, so I want to acknowledge the teachers of this School too, Dr. M. Bernaschi (Istituto per le Applicazioni del Calcolo *Mauro Picone*, CNR, Roma), Dr. G. Amati, F. Massaioli, M. Rosati, S. Meloni, L. Ferraro, P. Lanucara and G. Mambrini (<u>CASPUR</u>), Prof. J. Dongarra (Laboratory for Innovative Computing and Dept. of Computer Science, Univ. of Tennessee and Oak Ridge National Laboratory, USA).

# 2. High Performance Computing (HPC): what does it mean and why do we need it ?

It is nowadays commonly accepted that numerical simulations, based on mathematical models implemented in computational codes run on computing systems, constitute a third type of tools for scientific investigation, along with theory and *real-world* experiments (numerical simulations are sometimes called *in-silico* experiments).

Both *real-world* and *in silico* experiments are characterized by scaling issues: the scales at which you want to realize your experiments require different levels of resources (including money) and technology. The technological improvements of the last decades in the fields of Materials Sciences, Microelectronics, Computer Sciences, have led to the "dream" of higher possibilities in managing numerical simulations scaling issues than the ones in real experiments: as an example, today simulations of magneto-hydrodynamics phenomena of interests for the typical astrophysical scales are implementable, while similar lab experiments not.

This partially-realized "dream" has been, till now, fed by the **Moore's Law**, which synthesizes the leap in computing power in terms of the number of elementary CPU cycles per seconds ("clock frequency"). The improvements in memory technology is at the base of that "dream" too. However, some bottlenecks do exist: the Moore's Law will be no longer valid ten/twenty years from now, because physical limits in the manufacturing of semiconductor devices at the nanometer scale have slowly started to being reached and the promises of new technologies based on optoelectronics, organic materials or quantum information devices seem not realizable on the same industrial scale (at the moment I'm writing this report). Beyond this bottleneck, there is a gap in the performance improvements in CPU and memory technologies. However, this last problem, as we will see below, is partially at the basis of the diffusion of parallel computing, nowadays in the form of Cluster and Grid Computing, pushed forward by the last decade development of new technologies for networking, *in primis* the Internet ones.

Despite these and other bottlenecks, it is commonly accepted, within the scientific and technological communities, the fact that many problems, phenomena and processes can nowadays be realistically studied by HPC and that HPC resources are even more increasing at high rates.

An HPC system, whatever its architecture, can be defined as a computing system that exploits at its nearmaximum performance its resources in terms of hardware components (CPU, memory devices, communication buses, etc. ..), their integration and the implementation of algorithms in computing codes. Depending upon the scales and requirements of the problem to be solved, the architecture and resources of the HPC system used can change, but the basic idea of HPC is an efficient exploitation of all the resources of the system: a modern multiprocessor supercomputer can't be considered a HPC system without setups targeted to its architecture, components and specific features, otherwise its performance will be drastically reduced.

Top scientific, industrial and business problems requires high level computing resources, other problems, such as playing multimedia movies on desktop PCs, require lower level resources, but in both cases an optimization of the hardware resources is needed.

One possible measure of required resources by a computing job is the total number of basic CPUs operations required for its execution and it is usually functionally dependent on the dimensionality *n* of the data structures involved in the computation, according to different mathematical relations for different types of problems (power laws,  $n^{\alpha}$ , logarithmic laws,  $n \cdot \log(n)$ , etc.). Another measure is the total amount of work (RAM) memory required for the execution of the job.

As an example, I propose here the calculation of the required resources for the execution of a geophysical CFD (Computational Fluid Dynamics) simulation for weather prediction on a time interval  $\Delta T = 24$  hours regarding the whole Earth (this calculation was suggested by Dr. G. Erbacci during one of the first lesson at the Cineca Summer School on Parallel Computing, july 2004). This is one of the grand challenges of scientific and technological Research which has not been solved yet, due to technological bottlenecks. Table 1 below considers all the parameters involved in such a simulation.

The model is based on mapping the spherical surface of the Earth on a plane, considering a 2D grid with mesh step of 1 Km. Many (100) such 2D slices are considered, differing for the z-position (radial distance from the center of the Earth, the radius of such mapped spheres are approximately considered constant). Thus, it is a (2+1)D model of the Earth. The 6 variables in the model are: temperatute, pressure, humidity, three cartesian components of the wind velocity vector field. Each time step of iteration in the code corresponds to 30 actual seconds. *flop* means *FLoating point OPeration*. The total number of flops necessary for the calculation, per each time step and grid cell is dependent upon the numerical algorithm for the solution of thermo-fluid dynamics equations on the lattice. Each variable is considered a double precision floating point variable, 8 byte long (according to IEEE 754 standard for floating point arithmetics).

| Parameter                              | Value (dimension)            |

|----------------------------------------|------------------------------|

| Earth circumference                    | $4 \cdot 10^4$ (km)          |

| Earth radius                           | 6.370 · 10 <sup>3</sup> (Km) |

| Earth surface                          | $5 \cdot 10^8  ({\rm Km^2})$ |

| # of CFD model variables               | 6                            |

| # of bytes/variable                    | 8 (bytes)                    |

| Lateral resolution of 2D cells         | 1 (Km)                       |

| Time step value                        | 30 (sec)                     |

| Total # of flop per time step per cell | 10 <sup>3</sup> (flop)       |

| Total # of vertical slices             | 100                          |

Table 1: extimates of the basic parameters of a grand-challenge computing problem, the numerical simulation of weather dynamics of the whole Earth in order to predict it on a real-time interval of 24 hours, by the use of geophysical CFD (Computational Fluid Dynamics) code.

Making some simple calculations, it results that the total (minimum) memory required is  $2 \cdot 10^{12}$  bytes (2 Tbytes) and a total number of about  $3 \cdot 10^3$  steps is needed for a simulation of 24 hours of weather dynamics. The total number of flops required for such a simulation is approximately  $1.3824 \cdot 10^{17}$ . Considering that the highest peak flops power (according to the special list compiled every six month by HPC communities and presented at the URL www.top500.org) that have been ever reached is 280.6 Tflop/sec (IBM Blue Gene supercomputer, with 131072 processors), the whole simulation will be executed hypothetically in about 8 hours, which is not sufficient (it will leave only 16 hours of prediction per day !).

The total number of flops that can be executed each sec on a HPC system is considered as one of the standard parameters for classifying its performance. Up to 1990s, the main strategy for improving the performance of HPC systems built as massively parallel supercomputers was based on using the top CPU technology developed for the market, on improving the interconnection bandwith between the computing nodes and on rising the volatile and hard memory at their disposal. Today, that strategy is still valid but new approaches have been introduced, based on the idea of using idle time of off-the-shelf common desktop computers distributed in different geographic areas for executing complex jobs divided in small pieces among them. This is the paradigm of Grid Computing, a label which does mean a heterogeneous set of techniques for distributed computing.

While up to 1990s HPC systems were used by specific communities for specific tasks (scientific simulations, large scale enterprise database administration and use, industrial design, etc. ) and were usually built as clusters of computing nodes placed in specific buildings, the same technology and methodology has been used for developing similar small clusters or clusters of inter-networked desktop PCs. Nowadays, the HPC techniques and software is diffused among more distinct communities (small-medium enterprises, single Universities or Depts., hospitals, etc.). More attention has been dedicated to the improvement of software performance for exploiting the hardware features of such clusters or PCs.

From the perspective of a scientist with low levels of knowledge in Computer/Computational Sciences and Engineering, such resources, more accessible and distributed, are very useful for small/intermediate simulations. However, it becomes very important to have a little bit of knowledge of optimization techniques in order to adapt one's code to the resources available: a small cluster of PCs can become an intermediate HPC system (with an intermediate cost !) if the simulation codes are configured for best using its hardware components !

Optimization of the code starts at the source code level, goes through the machine code level using tools implemented in modern compilers, then continues with its parallelization for the use on multiprocessor systems. However, optimization procedures must be applied also to serial codes running on single desktop computers and this is starting point for the realization of a HPC code, as I try to show in this report.

#### **3.** Computers architectures

At the basis of classical (not quantum) computer architectures, there is a set of logical principles, first of all sequentiality of instructions to be executed by the computer, coded by an algorithm usually represented by a flow chart. Sequentiality of operations has been a strong performance limitation factor since the design of first electromechanical and electronic computers. Interaction and communication between processing units and I/O (Input/Output) units, memories and other devices need the execution of multiple instructions in a synchronous way.

The idea of parallel computing is simply based on the possibility of executing different instructions on different or same data at the same time, without excluding the use of a sequential algorithm. Technological and theoretical improvements in the last decades have followed two different ways for realizing parallelism in computing machines:

1. implementation of parallelism in the single CPU, the Central Processing Unit of a Von Neumann's-like sequential computer;

2. implementation of parallelism in a system made of many processing units (many CPUs) communicating data between them.

In the first case, the Moore's law trend (the number of transistors per square inch in microprocessors doubles every 18 months) and the design of new architectures for communication buses between CPUs and memory have pushed forward the performance of microprocessors. In the second case, the improvement in newtorking technology and the development of communication paradigms between computers (and consequent algorithms and softwares) have led to the construction of multiprocessor supercomputers. A combination of both features is at the basis of modern HPC systems.

#### 3.1 The Von Neumann's architecture and its bottlenecks

work volatile memory (RAM)

Figure 1 below schematizes the well know Von Neumann's architecture of a (sequential) computer:

Figure 1: basic logical schema of a CPU according to Von Neumann's architecture; in turkoise blue, the instruction register; in light green, the data register; in salmon red, the output register. Registers are small memory devices implemented within the CPU itself. The ALU is the operational core of the CPU: it can interpret and execute instructions which are arithmetic/logical operations between operands (data in binary format). The input and output units are interface devices between the inner and outer "world" of the CPU, while the control unit has a role of regulation and synchronization of operations.

The basic way of work of such a computer follows the subsequent list:

- fetching an instruction from the work memory (RAM) into CPU internal registers;

- computing the addresses of operands which are data stored in memory;

- fetching of operands from memory to CPU internal (data) registers;

- execution of the instruction (an operation on operands);

- storing of the result in a CPU internal register;

- transmission of the result from CPU storing register to memory.

The first bottleneck of such an architecture for information processing can be summarized as follows: "The instruction stream is inherently sequential – there is one processing site and all instructions, operands, data and results must flow through a bottleneck between processors and memory". Fetching data and instructions within

CPU registers from memory, interpreting instructions, executing them, communicating results to the memory: each of this operation can be executed one at time at each CPU "clock cyle". The Moore's law trend has led to a powerful increase of the clock frequency: from 100 nsec of the CDC 6600 (1970s) to < 1 ns for Intel Pentium (2000's) for each clock cycle. However, as cited before, the still existing gap between the improvement in microprocessors and memory technologies, the physical limits in raising clock frequency (mainly thermal dissipation, that increases with the increase of the number of devices integrated per square inch) are strong limits to further future technological improvements.

Other issues that influence the performance of sequential computers are:

• the bandwith of the communication buses between CPU and RAM: how many data (bit) per second can be moved from one device to the other; optoelectronics communication devices used within PC promise to raise data transfer velocity, but there are many physical limits, such as the use of semiconductor lasers integrated on-board with other electronic devices;

• the bandwith of the buses for the I/O communications;

• latency times between CPU, RAM and other units, i.e. each device has a different access time, so it is difficult to synchronize their correlated functions and usually it is not possible to use each CPU clock cycle for executing an operation, many clock cycles are used in waiting for data transfer from one unit to another.

Many solutions have been found in the last decade in order to overcome such bottlenecks and this has happened simultaneously with the development of theory and technology of multiprocessor computers. In the next Section, some of this solutions are presented.

#### 3.2 CPU built-in parallelism: technological improvements

Nowadays, the architecture of the CPU of a medium-level desktop PC maintains the basic features of the Von Neumann's one, but it is more complicated, with the addiction of many functional units that have improved speed (clock frequency), reduced memory access latency and realized some forms of parallelism. The top technology available today on the microprocessor market is based on the "**Dual Core**" architecture: two actual identical microprocessors with respective units are integrated in a single package, the clock frequency and control unit are the same for both. Instead of increasing the clock frequency of a single processor, two coordinated processors are used synchronously for the execution of different parts of a job or different jobs. In this way, the thermal dissipation associated to high clock frequency (up to 100 W) is contained and the performance is incremented.

The first Dual Core processor was introduced by IBM with the PowerPC model, in 2003. Intel and AMD, the largest CPU manufacturers of the world, proposed their Dual Core CPUs only in 2005 (Intel Pentium D and AMD Opteron may 2005 and Athlon 64 X2). Both vendors are involved in a large number of projects in order to realize multi-core CPUs, also with heterogeneous cores dedicated to different types of jobs (image and audio signal processing, mathematical calculus).

The Dual Core technology realizes parallel data processing at the scale of the basic unit of a sequential computer, the CPU, but requires dedicated and optimized software in order to exploit its potentialities: with dual or multi-core CPUs multi-tasking and multi-threading (executing more than one program at a time, concurrently, and executing different instances of different programs synchronously, respectively) can be fully implemented, but at the cost of more complicated software (e.g., particular compilers must be used on multi-core processors, otherwise programs are compiled for a single core CPU and only one unit of two is then used). The trade-off between complexity in compiler technology and performance improvement will show us if multi-core CPUs will be successful.

The way towards parallelism in the way of work of a CPU, however, has begun many years ago, with different technological solutions presented briefly below.

#### 3.2.1 Bit-parallel memory and arithmetics

Instead of reading one bit at a time of a CPU word from a memory location (as in the first electronic calculator, which was very sequential), it was introduced by IBM (1950s) a technology for reading blocks of bit from memory locations. Special bit-parallel memories were realized and integrated in mainframe calculators (IBM 704).

#### 3.2.2 Implementation of I/O-dedicated processors

In the first generation of computers, I/O operations were executed by the CPU itself. During the 1950s-1960s, IBM introduced dedicated I/O microprocessors which received I/O instructions from the CPU and then executed

them, freeing the CPU from such work. IBM 709 (1958) had 6 dedicated channels for I/O data, while CDC 6600 (1968) had up to 10 dedicated microprocessors that worked independently and asynchronously from the CPU for I/O instructions.

#### 3.2.3 Memory interleaving

Instead of using RAM memories which could be accessed only in a sequential way, a new technology was introduced since 1960s in order to subdivide them in different modules, each of which can be accessed independently from the other. A dedicated electronic circuitry was associated to each module, in order to parallelize the addressing to memory locations.

#### **3.2.4 Hierarchies of memories**

In the previous Sections, the gap between memory and microprocessor technology improvements has been cited as one bottleneck of the Von Neumann's architecture of computers: the time for the execution of a single instruction by a CPU is getting lower, the time required for the access of a single memory location by the CPU too but with different rates. Memory technology (both RAM and hard disk ones) has greatly improved in the last decades: modern hard disks can store tens/hundreds of GiBytes data, RAM memories can store up to Gwords; access time to RAM has got from 200 ns of 1980s to 50 ns of DDR models of 1990s. The time for direct access to hard disk is of the order of msec. Transfer of data from hard disk to RAM requires µsec.

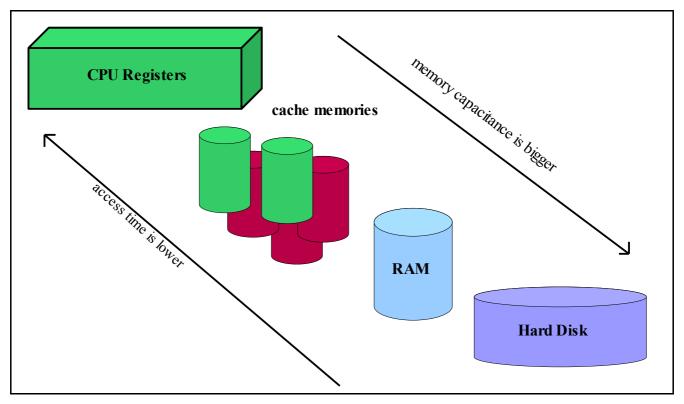

Despite technological improvements, the gap still limits the performance of modern computers. A solution for fighting against this limiting factor is buffering the data and instructions transfer from memory to the CPU using a hierarchy of intermediate memory devices which is schematically synthesized in Figure 2. Curiously, this type of solution was proposed for the first time in 1947 by the mathematician John von Neumann himself, but the memory technology did not have at that time the possibility to implement it in a useful way.

Figure 2: schema of the hierarchy of memory devices between the CPU and the hard disk (non volatile storage device). The cache memory devices are organized according to a specific hierarchy: devices with lower capacitance have lower access time and are "closer" to the CPU, while devices with more capacitance has longer access time.

Buffering data and instructions transfer means that part of them is stored at the intermediate levels between RAM and CPU registers after the first transfer: when they are used again, they are "closer" to the CPU, so time for data communication is reduced. Cache memory devices constitute this intermediate hierarchy and can be on-chip (built within the CPU) or off-chip. They are usually smaller than RAM memories (in terms of capacity) but with

lower access time. For example, the DEC Alpha 21164 CPU architecture has a clock frequency of 500 MHz, a level-1 (L1) on chip cache memory with 4 nsec access time, a level-2 (L2) cache with 5 nsec, a level-3 (L3) off-chip cache with 30 nsec and a RAM with 220 nsec access time. The Intel Pentium IV ....... *[insert some example of off-the-shelf CPU cache architecture]*

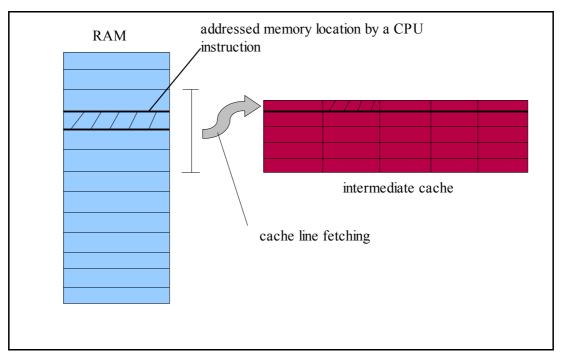

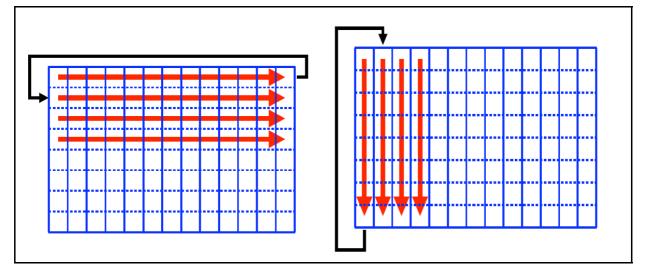

A cache memory device has a completely different architecture in respect of RAM or hard disk devices: it is divided into slots with the same capacity organized as *lines*. *k* subsequent memory locations can be mapped into each cache line. When a data is called from the CPU instruction, if it is not stored in the cache, it is fetched in a cache line location together with its near neighbour data, up to filling in a whole cache line (Figure 3).

Figure 3: schematic representation of the architecture of a cache memory device and of the cache line fetching mechanism, through which when some data is queried by the CPU, it is transferred from its RAM location into a location of a cache line along with the data that are contigous to it in RAM up to filling in a whole cache line.

When an instruction does modify a data (a variable, for example), if it has been pre-fetched in a cache location, it is updated both in the cache line and in the memory original location, according two possible methods:

- cache write-back, *i.e.* each data fetched in a cache line remains therein until the line is requested by an instruction for the memorization of new data; in that case, the updated content of the data is written only in its original memory location;

- cache write-through, *i.e.* data is updated synchronously in the cache and memory locations.

The increase in performance of a code depends on cache memories hardware features but also in the way the program has been written: for exploiting the properties of data transfer buffering through the cache hierarchy it is necessary to make use of local references in the source code, i.e. to declare and/or use variables involved in the same expression as closly as possible. There are two types of **local referencing**:

- **temporal**, when an expression or some variables in the source code are used many times at different points of the code;

- **spatial**, when addressing a memory location (for example through a pointer) is followed, in the code, by addressing one of its contiguous locations (for example, expressions involving the use of different elements of an array).

It is shown in the Sections below that the potentialities of data buffering through cache hierarchies are exploited following some rules in designing the algorithms at the base of the source code and using some special optional flags of optimizing compilers, which act at the Assembly and machine level code translation.

There exist both data and instruction cache memory devices: instructions can be fetched into cache lines and the CPU can fetch them from there instead from RAM. This feature is very useful when a code makes an iterative use of the same instructions, diminishing the time of execution because the same instructions are recovered directly from the cache line when needed.

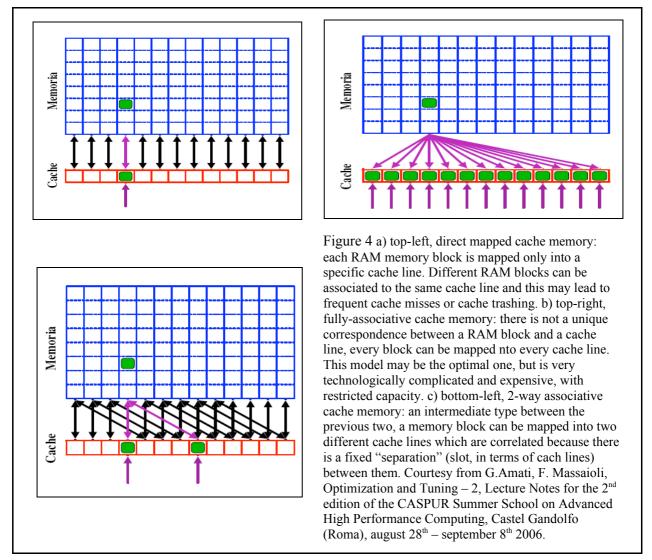

The increase in the performance of a code also depends on the method with which RAM memory locations are mapped into cache lines (see Section 4.2 for the optimization techniques at the source code level in order to take advantage of the cache hardware features). According to this feature, cache devices are subdivided into three groups:

- direct mapped cache;

- fully associative cache;

- set associative cache.

The **cache direct mapping** is the straight-forward way of mapping: subsequent memory locations are mapped into a cache line up to its filling such that every memory block has a direct correspondence to only one cache line. This method is not completely optimal: when the first cells, respectively, of two memory blocks completely mapped into the whole cache are repeatedly required by a CPU instruction, the entire cache must be re-fetched with the appropriate block, the required data may be not immediately at disposal in the cache, then a **cache miss** happens. Cache misses cause a special kind of **overhead** called **cache thrashing**: a whole cache line may be wiped out before it has been accessed only because an instruction asks for an address which is mapped at the beginning of a new set of blocks which completely fill up the cache itself. Among the advantages of direct mapped caches there is the possibility of arbitrary capacity, simple algorithms to substitute values into the locations and a simple method for finding an element in the cache, i.e. to realize a **cache hit** (some bits of the memory address refers to the cache line where that element can be found).

The **fully associative mapping** let a general memory location to be mapped into a general cache line, without following strictly the sequence of data in memory. When a CPU instruction asks for data in a memory location, the corresponding data is firstly searched for in **every** cache line: if it is found, it is transmitted to the CPU registers, otherwise a cache miss signal is transmitted. This mapping method makes use of specific types of cache devices based on an associative memory technology, which is expensive and complicated but necessary for finding an element fetched into the cache. The higher cost of production of a fully associative cache in respect of a direct mapped one limits their memory capacity. The algorithms used for the substitution of data into a location are very complicated too or not efficient: usually a FIFO (First In First Out) approach is used, so the line less used is the one where new data is transferred from the RAM or other cache devices.

Finally, the **set associative** method is a kind of direct mapping replicated on different slots such a type of cache is divided into. This type of cache device is usually made of 2 or 4 slots (two-way or four-way set associative). That means that a memory block can be mapped in a cache line on a slot or in the corresponding cache line of another slot (2-way associative). This method and corresponding technology let data located in different memory locations to be mapped into a similar cache line but in different slots, in order to avoid cash thrashing overhead. This type has been introduced in order to balance between the complexity of electronic circuits needed for the fully associative approach and the low fault-tolerance of the direct mapping one.

Usually, all cache memory devices are set associative: L1 cache  $4 \div 8$  way set associative; L2,L3  $2 \div 4$  way set associative or sometimes direct mapped in order to have more capacity. Figure 4a, 4b, 4c show schematic representations of the three respective different methods of mapping between RAM memory and a cache device.

#### 3.2.5 Multitasking

Multitasking has been one of the most important technological solution introduced in CPU functionality in order to go beyond the strict sequential model of the Von Neumann's architecture: the execution of a job is made by a sequential set of instructions, i.e. computing and I/O operations; during the I/O operations the CPU is idle, waiting for data communication; instead of leaving it idle, the CPU can be charged with instructions of another job. This is a first example of built-in parallelism: many pieces of different jobs (programs) are executed simultaneously. A particular type of multitasking implementation is **time sharing**, that is the concurrent execution of different programs by different users letting each user to interact with his/her-own process (CPU bursts of activity are used for each program).

#### 3.2.6 Instructions look-ahead

Instruction look-ahead is another technological solution developed for breaking the strict sequentiality of Von Neumann's architecture: the decodification and memory localization of an instruction is made ready for the CPU before it needs or requires it according to the flow of the algorithm. In this way, the performance of the CPU with multiple function units is improved (see subsection below). This methodology is implemented at the Assembly code level by the activation of optional flags of compilers, which reorganize the structure of the source code into a

#### **3.2.7** Multiple function units

A leap toward CPU-level built-in parallelism has been the subdivision of CPU components in different devices dedicated to specific functions that can be executed indipendently. For example, in older computers, the CPU contained general registers (data and instructions), special registers (e.g. the program counter), the control unit and the ALU (Arithmetic Logic Unit). This last microprocessor was responsible of any type of calculation, one at a time. In modern CPU architectures, the ALU is divided into distinct microprocessors dedicated to distinct functions (boolean algebra calculations, fixed and floating points computing, etc.). The compilers are able nowadays to translate a source code in an optimized object code whose instructions flow is structured such that different calculations are made by the different units. However, the exploitation of this type of parallelism implies a correct use of the compiler, which must be customized to the specific CPU architectures. Modern compilers, as the reader can find below, are targeted to different architectures using optional flags.

#### 3.2.8 Pipelining

The pipelining is a general method of work subdivision and management, implemented in a CPU: a task  $T^i$  (flow of instructions) is divided into many sub-tasks  $T^i_j$  (different sets of instructions or single instructions); the flow is divided into different stages  $S_k$  too; at each clock cycle, only a sub-task can be executed. At time step 1 (1<sup>st</sup> clock cycle),  $T_1^{I_j}$  is executed within  $S_I$ ; at time step 2 (2<sup>nd</sup> clock cycle),  $T_2^{I_j}$  is executed within  $S_2$ , but instead leaving  $S_1$  idle  $T_I^2$  is executed within it, and so on at subsequent clock cycles. In this way, the task  $T^I$  can "flow" through the different stages  $S_k$  of the CPU without leaving idle the stages, which begin executing sub-parts of other task  $T^i$ . It should be noted that there is a sequentiality in the sub-tasks execution:  $T^i_j$  can not start if  $T_{j-I}^i$  has not finished.

The schema of a CPU or dedicated microprocessor which implements pipelining is represented in Figure 5.

Figure 5: logical schema of a CPU implementing pipeling. The pipeline is made of a sequency of elaboration devices (stages  $S_k$ ). Each stage makes calculations (boolean or arithmetic) on different parts of data/instructions. Between each couple of stages, there is a **latch** device which acts as a kind of register for local intermediate data to be passed from a stage to the other (the output of a stage is the input of the subsequent). Data/instructions flow into the pipe according to a clock signal which regulates the execution of a sub-task in a stage and the transmission of data from a stage to another.

Pipelining is a fundamental methodology for reducing idle time of microprocessors and is very useful in linear algebra arithmetics (array arithmetics), because it requires the execution of the same operation (for example a sum of floating point variables in the case of the sum of 2 1D floating point arrays) many times on different sets of operands. If each stage runs a part of that operation, at each clock cycle (except the first and the last) such parts are executed on respective components of the different arrays.

#### 3.2.9 Floating point arithmetic: SIMD technology

Most common off-the-shelf PCs CPUs belong to the x86 (or 32 bit) architecture class, also called IA\_32 referring to Intel 32 bit architecture (one of the most famous and diffuse). 32 bit architecture means that the basic "words", with which instructions are codified, are 32 bits long.

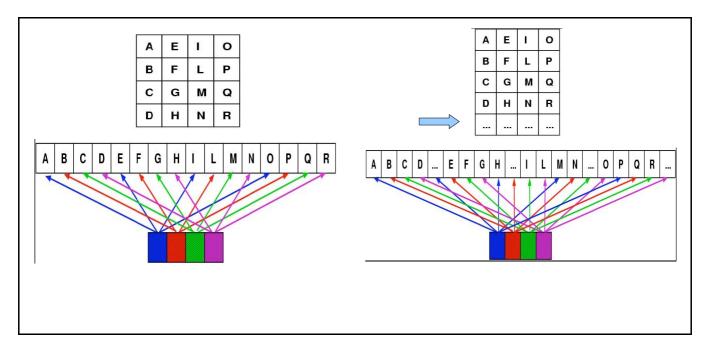

Since 1970s, computers have been more and more charged with new types of data elaboration involving multimedia data (signals, images). Computer Graphics has started to be improved since then. Multimedia processing and Computer Graphics usually require the execution of the same type of operation (mainly a mathematical one) on a huge amount of data of the same type. For example, in Computer Graphics, operations such as geometric transformations need to be applied to large sets of homogeneous data (fixed or floating point variables representing vertices). In multimedia applications, a common operation is the change of the brightness of an image (i.e. a 2D map of values). Three variables are associated to each pixel of an image, indicating the level of red, green and blue colors, respectively, according to a common scale. To change the brightness of the image, a same value must be added or subtracted to each variable of each pixel (grid point in the 2D map).

A technique and corresponding technology to realize the execution of the same operation on a large amount of data of the same type using only one instruction was developed along the 1970s and 1980s for dedicated parallel supercomputers (vector and array processors) (see Section 5 for the Flynn's classification scheme) and for dedicated microprocessors or functional units, for example DSPs (Digital Signal Processors) or GPUs (Graphics Processing Units): it is called the **SIMD** (**Single Instruction Multiple Data**) technology. The same principles and corresponding technology have been implemented in off-the-shelf CPUs in the last decade, with different solutions, in order to satisfy first the needs of multimedia and graphics processing.

In 1997, Intel introduced in the desktop PC market the first architecture with SIMD capabilities, the Pentium **MMX (MultiMedia eXtension)**. These extensions use new commands to perform two, four or even eight integer instructions in parallel, which are commonly over-used in image processing. The MMX architecture uses the **FPU** (**Floating Point Unit**, one of the functional units cited in Section 3.2.7) to load the data adjacently into registers, using 64 of the 80 bits of each FPU register (8 per CPU, also known as x87 registers). In this way, the programmer has to decide between common x87 or MMX instruction sets for floating point arithmetics and this can be done by inserting Assembly language instructions in the source code.

In 1999, Intel released on the market the Pentium III architecture, including 8 new dedicated registers and 70 new Assembly language instructions to perform single precision floating point computation using SIMD techniques. Such extension is called **SSE** (**Streaming SIMD Extension**) technology. Each new register is 128 bits long and is labeled xmm*i*, where i = 0, 1, ..., 7. In 2000, Intel introduced the first versions of Pentium IV with a new extension of SIMD features, **SSE2**, with a set of new instructions for handling with double precision floating point calculations, exploiting the power of the xmm*i* 128 bits registers, each of which can contain 2 double precision FP numbers. In this way, the applications requiring massive FP computing, such as those of Computer Graphics or Scientific Computing, has found place also on off-the-shelf desktop PCs.

AMD, the other more important CPU and microprocessors manufacturer, has developed its own SIMD extensions to the x86 architecture and has called it **3DNow!**. This technology adds (single precision) floating point capabilities to MMX architecture, extending the Assembly instruction set.

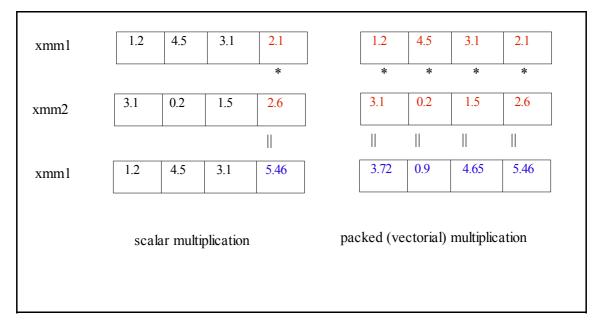

MMX, SSE, SSE2 (and successive new extensions, nowadays called SSE3 and SSE4 in the last Pentium IV versions) and 3DNow! have their own Assembly instruction set. Each specific instruction can be **scalar** or **packed**: scalar instructions are the common Assembly ones applied to the least significant element of a vector, which can be contained in the large 128 bits xmm*i* registers; packed ones simultaneously apply to all the elements of the vector. Figure 6 illustrates a scalar and packed multiplication of single precision FP variables, which can all be stored contigously in a SSE register.

Figure 6: schematical representation of scalar and packed SSE multiplications. 2 SSE registers are used for the two sets of operands (in red), xmm1 and xmm2. In this case, the SSE multiplication is made between single precision FP numbers, coded as 32 bit long strings. Each SSE register can contain 4 such values, that is a 1D array of length 4. The scalar multiplication is a multiplication between the last elements of the respective arrays (registers) and it produces a new number stored in the same register position (in blue), while the packed multiplication is a per-element operation, so it produces 4 new values.

Despite the possibility of vectorial (so parallel) floating point arithmetics operations, there are some bottlenecks in the use of SSE/SSE2 instruction sets: the programmer must pay attention to how the program organizes data into memory, because loading data into SSE registers requires they occupy contigous memory blocks that start and end on 16 bytes borders (**data alignment**). This means that software development must be tuned to SIMD architecture, otherwise the usual FPU instruction set and registers are used for floating point arithmetics: a Pentium IV then makes floating or fixed point calculations with the same performance of a Pentium or 80386 !

High level programming languages do not specify standardized SIMD functions. SSE-aware object code relies on the capabilities provided by the compiler or on the possibility of introducing Assembly language instructions within the source code. In the first case, the code can be **automatically optimized** for SIMD instructions by invoking special option flags of the compiler. Most of modern compilers have these capabilities: the dedicated flags are reported in Section 4.3 for GCC and in Section 4.4 for the Intel compiler. In the second case, there are some languages, such as C/C++, that permit to introduce Assembly instructions in the source code, so a **manual optimization** can be realized. Figure 7 illustrates a piece of C source code in which a function for the scalar product of two vectors is defined. The source code presents both a usual implementation (left column) and a modified version (right column) containing Assembler instructions which do refer to SSE registers. In the second case, the programmer must be a little bit aware of CPU Assembly language and instruction set in order to use them.

```

01 //Compute scalar product

between two vectors in C

02 float

scalarproduct(floatx[],floaty[])

03 {

04 return x[0]*y[0] + x[1]*y[1]

+ x[2]*y[2] + x[3]*y[3];

05 }

```

```

01 //Compute scalar product

between two vectors in C

using Assembler instructions

02 float

scalarproductAssembler(float

x[],float y[])

03 {

04 vector temp;

05 asm(

06 "movl

%1,

%%esi;"

07 "movl

82,

%%edi;"

08 "movaps (%%esi), %%xmm0;"

09 "mulps (%%edi), %%xmm0;"

10 "movaps %%xmm0, %0;"

11 : "=g"(tmp)

12 :"r"(x),"r"(y)

13);

14 \text{ return tmp.f[0]} + \text{tmp.f[1]}

+ tmp.f[2] + tmp.f[3];

15 }

```

Figure 7: comparison between two C source code typescripts defininf a function that returns the scalr product of two vectors. The left column typescrit is a typical C code: the output of the function requires 4 additions and 4 multiplications between single precision variables. The right column typescript shows the definition of a similar function which makes use of Assembler instructions within the asm(); function call: line 6 means "move the first operand in the register "esi"; line 7 means "move the second operand in register "edi"; line 8 means "move the content of register "edi" in the register "xmm0"; line 9 invokes the mul instruction executed in packed mode (p) and on single precision floating point data (s), so mulps; the instruction is a multiplication element by elemeny of the data in the two registers. Than teh result of the packed multiplication is placed in register xmm0 and then moved to register %0. The structure tmp of type vector then receives the output of the asm(); function. As can be seen, 4 additions are still needed, but only one instruction for the multiplication, a packed instruction instead of a scalar one. Courtesy from [Siemen2003b]

Manual tuning of the code to the CPU architecture, using Assembler instructions, is very difficult, leads to a complicated source code and requires technical knowledge of the Assembly language of the used CPU. Scientists using computers for computing may not have such knowledge or possibility to obtain it. However, manual optimization is the best way in order to adapt your code, piece by piece, function by function, for using completely and in a performant way the hardware resources. For these reasons, CPU manufacturers, such as Intel, usually provide intrinsics, that is special data types and functions, collected in libraries, which are C compiled versions of Assembler instructions. This is an intermediate solution between the use of pure Assembler and the use of automatic optimization by compiler. This last solution is more user-friendly but it usually makes the code less performant. However, it is the most widely used in the Scientific Computing communities and for this reason it is presented in Sections 4.3 and 4.4 for two different compilers. It should be noted that modern compiler manufacturers (Intel, Portland Group) or developers (GCC initiative community) have been increasing the number of optimizing flags at disposal of the user for many types of architectures. The important thing is a correct exploitation of such flags by the user when he/she compiles his/her programs and this implies that he/she must know a little bit of the hardware architecture of his/her desktop PC (or parallel supercomputer) and must make an extensive use of the manual of the compiler used. These requirements are not so considered by scientists who use computing facilities as tools for obtaining scientific results.

#### 3.2.10 CPU design "philosophies": past and future sceneries

The previous list of theoretical and technological solutions for improving the performance of CPUs must be considered in a more general framework of basic design philosophies developed and implemented in the last decades by the Microelectronics and Computer Science Research communities and manufacturers.

#### 3.2.10.1 CISC and RISC architectures

CPU architectures are usually classified as belonging to 2 different families: CISC (Complex Instruction Set Computer) and RISC (Reduced Instruction Set Computer).

The **RISC** architecture is the one used in the most diffused microprocessors and microcontrollers (i.e. for embedded computers) and is based on a philosophy that favours a simpler set of instructions (at the Assembler level) which all take about the same time to execute.

In the early days of the computer industry, CPU designers tried to make instructions do as much work as possible: for example, one instruction that would do all of the work in a single operation, i.e. loading up two numbers to be added, adding them, then storing the result back directly to memory. At that time, there were two types of reasons for such a design philosophy, called **CISC**:

- compiler technology did not exist, programming was done in either machine code or Assembly language; to make programming easier, complex and integrated instructions that implemented a whole set of successive operations were very useful;

- memory devices were, at that time, very expensive, small (in term of capacity) and slow (in terms of access time), it was advantageous to store information in computer programs instead of memory.

The complex instructions of first CISC CPUs were direct representations of corresponding high level functions of high level programming languages. They were inspired by a general principle called "orthogonality principle": to provide every possible addressing mode for every instruction. Beyond this, it should be added that during 1960s-1970s, built-in CPU registers were very expensive and difficult to be integrated on chips, so CPUs had to communicate mainly with RAM devices: decreasing the frequency of access to RAM was a must, so complex instructions seemed to be a good solutions to such issue.

However, in the late 1970s, researchers (mainly at IBM) demonstrated that many features of such CPU instruction sets, designed for faciliting coding, were ignored by real world programs and the instructions themselves took several processor cycles to be performed. In those years, advances in theoretical Computer Science were leading to new technologies in writing compilers. Such early stage compilers did not take advantage of such instruction sets. Most of these instructions were not used frequently by developers, so CPU designers did not care tuning them and the result was that they were slower than a number of smaller (but simpler and tunable) operations doing the same things.

CISC architectures were complicate to be implemented into hardware and did not leave empty space for registers and built-in caches, memory devices which were being introduced in those years and which were even more useful for facing the bottleneck of frequency clock-RAM access time gap. Many analyses showed during the 1970s and 1980s that very used constants in common programs would fit in 13 bits, while almost every CPU design of that time dedicated some multiple of 8 bits for storing them. So, in order to decrease memory access frequency, instructions might be implemented with a smaller number of bits, leaving room for constants coding. Other studies confirmed that real-world programs spent most of their time executing very simple operations, so the most used ones should be implemented as simple and fast instructions: the goal, at that time, was 1 instruction in 1 clock cycle.

These issues led to the RISC design philosophy, which has one advantage over the CISC one (less need to use registers or memory space because data can be embedded in instructions) and one disadvantage (a simple task is run as a series of simple instructions, but the total number of instructions read from memory is larger, therefore takes longer).

Some technological advances towards built-in parallelism (pipelining, embedding multiple function units in a single chip, see Sections 3.2.7 and 3.2.8) introduced in the 1980s seemed to favour the RISC approach, because the core logic of a RISC CPU requires fewer devices and leaves more free room for other devices.

In fact, many academic, then industrial, projects were devoted to the development of RISC architectures. The most famous ones were:

- DARPA VLSI project;

- UC Berkeley's RISC project (1980), which led to the RISC-I and RISC-II prototypes, this last one being used as the basic model for nowadays RISC microprocessors;

- Stanford University MIPS program (1981) which led to the MIPS design used for commercial applications in Computer Graphics consoles (PlayStation and Nintendo 64) and common embedded processors for high-

end applications;

• IBM Power (1990s-2000s) and PowePC (2000s) processors, which are the most famous RISC processors used on mainframes, IBM supercomputers and dedicated embedded microprocessors (e.g. for the automotive industry).

Despite its succesful characteristics and tendency to support the integration of the CPU built-in parallelism solutions, the RISC design philosophy has not managed to become the standard in each field of microprocessors design: the CISC architectures still are the most diffused in the desktop PC, high performance supercomputers (except for IBM's ones which make use of Power technology) and commodity servers markets. While RISC processors dominate the market of mainframes and of embedded CPUs and controllers, the x86 architecture (a CISC one) remains the *de facto* standard for desktop PC, for three main reasons:

- the very large base of proprietary PC applications are written for x86, whereas no RISC platform has a similar installed base and this has meant that PC users have been locked into x86 despite lack of performance;

- RISC architectures have been able to scale up in performance quite quickly and cheaply, but Intel and AMD (the most powerful microprocessors manufacturers) have taken advantage of their large markets for spending enormous amounts of money on processors development and improvements;

- Intel and AMD designers has managed to apply some features of RISC design philosophy to x86 architectures: for example, the P6 core of Intel PentiumPro and its successors have special functional units that expand and "crack" the majority of CISC instructions into multiple simpler RISC-like operations.

The resources of Intel and AMD in supporting their x86 products have been so high and uncomparable with the ones of pure-RISC manufacturers that today x86 CPUs are more performant than RISC ones, except for IBM Power and PowerPC processors, which are good competitors.

#### 3.2.10.2 VLIW (Very Long Instruction Word) CPUs

The **VLIW** architecture was first proposed in the arly 1980s by J. Fisher at Yale University. It describes an instruction set philosophy in which the compiler packs a number of simple, non-inter-dependent operations into the same instruction word. When fetched from cache or memory into the processor, these words are easily broken up and the operations dispatched to independent execution units. This approach to CPU architectures can be described as a software- or compiler-based superscalar technology.

Nowadays, the most diffused CPUs with a VLIW architecture are the ones belonging to the **x86\_64 family** or generally the 64-bits processors. Up to 2005, the 64-bit CPUs have been used on servers, multiprocessor supercomputers like clusters of PCs and also desktop PCs. The first 64-bit CPU was introduced in 1991 by MIPS. In 1994, Intel announced the successor of its x86 technology, the **IA-64** architecture, effectively released on the market in 1998-1999 with the Intel Itanium. In the same year, AMD announced its 64-bit solution, which is now known as the x86\_64 architecture, copied by Intel in 2004 with its **EM64T** platforms. In this case, AMD was the winner in the run towards 64-bit CPUs for desktop computers, with the AMD Opteron and AMD Ahtlon 64. Also IBM has dveloped some lines of its PowerPC processors using the 64-bit technology.

64-bit architecture first of all means that the integer registers of the CPU are 64 bits long. These registers can contain the values of pointer variables, used for addressing the RAM or the virtual memory. In a 32 bit architecture, the amount of memory space that can be addressed is no more than 4 GiBytes. This has been an unreachable amount of memory up to some years ago. Multimedia, scientific computing or large-scale database applications today require many GiBytes of real or virtual memory and such memory devices are now available on the common market place.

A CPU with 64 bits long words (coding of instructions) is also more performant in pointers, fixed point and floating point arithmetics. However, it requires dedicated drivers, compilers and operative systems (OSs). One major problem with its introduction in the market place is the compatibility of software, mainly written for 32 bit architecture. Most x86\_64 processors guarantees a hardware-implemented compatibility with x86 software, because the 32 bit instruction set is still supplied with the new one.

#### 3.2.10.3 SMP (Symmetric Multiprocessor) and Multi-Cores computers

Section 3.2 is dedicated to technological solutions for implementing different forms of parallelism within the CPU itself. Although the described technologies and methodologies have led to performance improvements which could not be imagined years or decades ago, many physical limits have been reaching in the integration of semiconductor devices in single chips. It seems that CPU built-in parallelism has been pushed forward as much as possible, so computers manufacturers are trying to extend multiprocessor architectures typical of supercomputers

also to desktop and server ones.

A SMP (Symmetric MultiProcessor) computer is an hardware architecture very well known in the field of parallel computers: on a single board, many CPUs are implemented, sharing the RAM memory. Such an architecture is also called **shared-memory parallel computer** (see Section 3.3.2.1) and it has been shown that its performance scales down with more than 16 processors, due to the difficulties in the management of memory access by the different units. A SMP architecture requires dedicated software, written with specific tools for implementing multi-threading programming techniques.

Many expectations have arisen in the last two years about new technologies which let the integration of two CPUs, with their respective inner caches, in a single chip/package. In such a way, two processors can function at the same clock frequency, increasing computational power without increasing power dissipation (which are nowadays of the order of 100 W) and device temperature. Such an architecture has been called **dual-core** and was first introduced in 2003 with the IBM PowerPC models. Both Intel and AMD released their first versions of dual-core processors in 2005 and their plans for the future are addressed towards **quad-core** processors (4 CPUs in a single package). There are also projects for heterogeneous multi-core processors, where each core is a CPU dedicated to specific type of data processing (image processing, audio processing, mathematical computing, etc.). Desktop computers based on dual-core processors are yet on the market: Intel Pentium D and AMD Athlon 64 X2 and FX60 are the last ones released by the two manufacturers in 2005-2006. Such computers require OSs specifically developed for their architecture and dedicated compilers and this seems to be the major drawback at the moment for their diffusion, also in the HPC field. However, they are symptomatic examples of the future plans of CPU manufacturers: new forms of parallelism are investigated and searched for, in order to overcome the limits inherited by the Von Neumann's architecture.

#### **3.3 Parallel (multiprocessor) computers**

A parallel computer has been theoretically defined as *a large collection of processing elements that can communicate and cooperate to solve large problems fast*. According to this definition, a single modern CPU can then be considered as a parallel computer due to its architecture based on multiple function units (see Section 3.2.7). However, the processing elements cited above are the CPUs.

**Parallel computing** is a computing approach devoted to solve a single problem (through the execution of a program) subdividing it in many homogeneous or heterogeneous sub-problems to be solved by the single CPUs (processing units) simultaneously. The complete original problem solution is guaranteed by the **communication beetween the different processing units**.

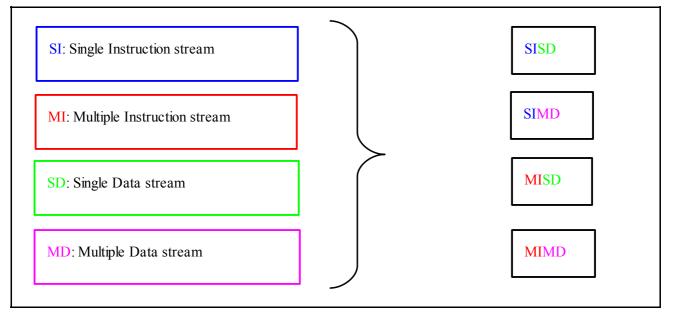

A classification scheme of computer architectures was proposed in 1966 by M. J. Flynn [Flynn1972] and it is still used also for introducing the different types of parallel computers architectures. This scheme is based on two criteria: the distinction between **instruction stream** (sequence of instructions to be executed) and **data stream** (sequence of data over which instructions act); the molteplicity of hardware used for processing instruction and data streams. According to these criteria, there are four possible types of computer architectures resulting from the combinatorial association of different ways of instruction and data stream management. Figure 8 shows the management types and the result of their combinations.

The SISD architecture corresponds to the classical Von Neumann's one: a scalar computer with only one CPU without possibility of pipelining. The MISD architecture has never been extensively implemented, apart from some small Research initiatives. The SIMD architecture have been already considered in Section 3.2.9 regarding the implementation of some of its principles to single CPU architecture, but there we mention that these ones were inspired by multiprocessor architectures. Finally, MIMD configuration is the one more diffused today in the field of supercomputers.

#### 3.3.1 SIMD systems

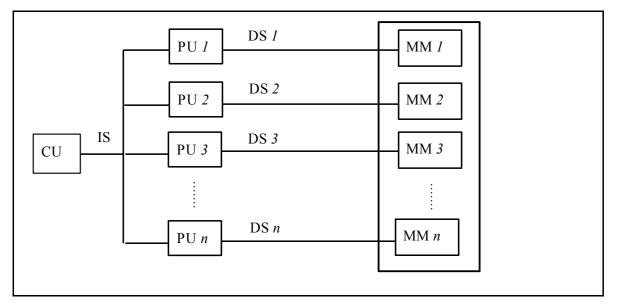

Figure 9 shows the basic schema of a SIMD multiprocessor computer, implementing a special kind of parallel computing model called **synchronous parallelism**.

Two main types of SIMD supercomputers were manufactured in the last decades:

**array processors**, made of a set of identical processing units operating simultaneously on different datasets; they were commercialized during 1970s-1980s and were very performant with vectorial calculations (each processing unit executes the operation on a component of the vector); some of them were realized as independent machines, while other types were modules to be integrated in other computing environments (**attached array processors**);

vectorial supercomputers, characterized by an extended instruction set containing vectorial

instructions to be applied to array-like data sets; they had specialized functional units able to implement vectorial operations, through the exploitation of pipelining (see Section 3.2.8); one of the most successful was the Cray 1, developed in 1976 by S. Cray.

Figure 8: representation of the four different types of computer architectures according to the Flynn's schema [Flynn1972]. The four categories are the result of all the possible combination of two different types of data stream management and two other distinct types of instruction stream management. The MISD model has never been implemented at the industrial scale, only some academic projects focused on certain issues tried to realize such a type of CPU.

Figure 9: basic general schema of a SIMD multiprocessor supercomputer. A single Control Unit (CU) distributes a single Instruction Stream (IS) to *n* Processing Units (PUs) (in general CPUs). Each PU executes that sequence of instructions on a different Data Stream (DS), i.e. on a different data set obtained from a distinct Memory Module (MM). In this way, a single operation is simultaneously applied to different data (synchronous parallel processing).

Among the most performant SIMD parallel supercomputers, we should aknowledge:

the **Connection Machine** by Thinking Machines, which, in its 2<sup>nd</sup> version, has 64K processors; it was released in 1987; each processor was directly connected to a local memory; groups of 32 processors might optionally share floating point accelerator units; this supercomputer was famous for its esterior design, for the possibility of arranging blocks of processors according to specific types of interconnection topologies corresponding directly to topologies of data structures on which parallel programs needed to operate;

during the 1980s and beginning of 1990s it was a leading example of supercomputer, appearing also in scenes of science-fiction movies like Jurassic Park;

the **APE** massively supercomputers, developed by an initiative of the Italian National Institute for Nuclear Physics (INFN) and commercialized during 1990s by QSW (Alenia S.p.A) under the name Quadrics; the project APE100 led to a parallel supercomputer with a peak power of 100 Gflops, which was a significant level for those years.

#### 3.3.2 MIMD systems

MIMD (Multiple Instruction Multiple Data) computers were the further development of the parallel SIMD ones. During the 1970s, the first big multiprocessor mainframes entered the market (Univac 1100/80, 1976, Burroughs B-7800, 1978, Cyber 170/720, 1979, IBM 3081, 1980). They still were affected by residual bottlenecks deriving from the Von Neumann's architecture: only the management systems of the multiprocessor architecture obtained a performance leap, because the number of jobs completed per unit of time increased. However, the usefulness of multiprocessing consists in the possibility of using independently or correlately the CPUs at the same time (parallel processing) and not assigning to each CPU a different job to be executed in a certain intrinsic time different from job to job.

MIMD architectures are theoretically divided into

• **multicomputer systems**, i.e. a set of interconnected but autonomous computers, communicating between them for exploiting parallel processing;

• **multiprocessor systems**, i.e. a system where many CPUs share together the same work memory. Nowadays, supercomputers are hybrid architectures, i.e. at certain scales units can be individuated and classified as multiprocessor systems, but at higher scales these units are integrated within a multicomputer architecture. The first class is also labelled **distributed memory architecture**, the second one **shared-memory architecture**.

Both types (or hybrid ones) supercomputers can exploit parallel processing, according to different paradigms which will be discussed in Section 5.1. Since the beginning of 1990s, new types of supercomputers have been classified and proposed within the class of distributed-memory systems: they have been called "**computing grids**" in analogy to energy transport grids. Multicomputer systems are usually tailored for scientific, industrial or business-management applications, located in a single building, their computational units are CPUs with their RAM memories integrated in large boards called chassis. Each chassis can contain many CPUs and centralized hard disks shared between them. Many chassis are then collected in a single "armchair" (see Figures 10-11 for a typical example of distributed-memory supercomputer), a **cluster supercomputer**, thus called because many single computers are "clustered" in a single case. Computing grids, however, are made of single computers (sometimes off-the-shelf desktop PCs) interconnected by LAN or WAN or Intranet and located in different rooms of a building or in different regions of the Earth. There is no complete agreement in HPC communities (both industrial and academic) on the terminology to be used: some computing grids are called clusters of PCs. However, two main differences characterizes the two types of distributed-memory systems:

- traditional cluster supercomputers have homogeneous computing nodes (i.e. chassis, sets of identical CPUs), interconnected by dedicated internal networks;

- computing grids usually are made of heterogeneous computing nodes, for example different PCs, thus the interconnection system is of more general type, a LAN or directly the Internet.

#### 3.3.2.1 Shared-memory architectures

Multiprocessor architectures are generally made of a limited number (from 2 to 32) of very powerful CPUs that share the same RAM memory. The memory access is coordinated and uniform: each CPU is characterized by the same access time for a generic memory location. The interconnection between memory and CPUs is realized through three different types of systems: common bus, crossbar switch or multistage network. Each CPU may have a local cache.

The SMP (Symmetric Multiprocessor) architecture described in Section 3.2.10.3 is an example of sharedmemory supercomputer. Such machines are sometimes called **tightly coupled systems**, because all the resources of the whole system are shared between the different CPUs. This type of architecture may be subdivided into two different sub-sets:

• UMA (Uniform Memory Access) architecture, when each CPU sees a common space of memory addresses and has the same access time to it (as previously said); this is the typical architecture of a SMP; if the implementation of this architecture implies that when a CPU updates the content of a memory location the whole system updates the values contained in each location of a cache memory device of a CPU

mapped into that memory location, then that machine belongs to the sub-category of **Cache Coherent UMA** (**CC-UMA**) SMPs;

• NUMA (Non Uniform Memory Access) architecture, when many SMPs are interconnected between them such that each CPU of a SMP can have direct access to the RAM memory of another SMP, with different cross access times, which are obviously larger than the CPU's access time to its local RAM memory; also in this sub-case, some implementations are classified as Cache Coherent NUMA machines, due to the same mechanism of global updating of cache memories of each CPU of each SMP. For the parallel programming of such small supercomputers, see Section 5.1.2.

Figure 10: an example of small cluster supercomputer, made by 8 chassis each containin a "computational node" made of 2 AMD Opteron 242 CPUs sharing a memory module of 1 GiBytes. Each computational node is a small SMP and is interconnected with the other by a dedicated 1 Gigabit internal network. This hybrid cluster computer is installed at the Bioinformatics and High Performance Computing Lab of the Bioindustry Park of Canavese (*http://www.bioindustrypark.it/*).

Figure 11: an example of a large scale cluster supercomputer installed at Cineca. It is an IBM Linux Cluster 1350 made of 512 IBM X335 computational nodes. Each computing node contains 2 Xeon Pentium IV CPUs that share together 2 GiBytes of work memory. Each black "armchair", also called rack, contains many chassis, each chassis contains a certain number of computational nodes.

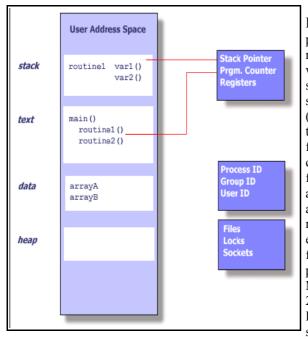

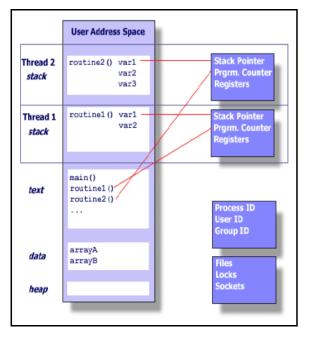

#### **3.3.2.2 Distributed-memory architectures**